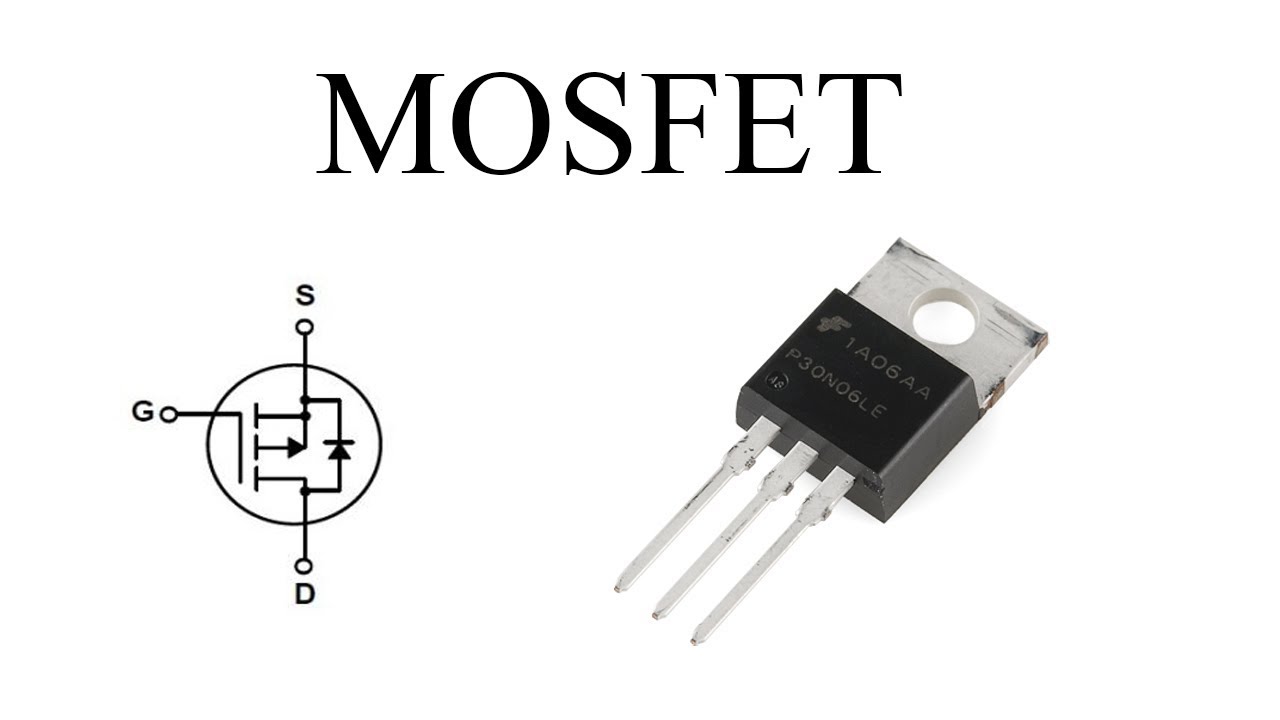

I transistor MOS ( Metal Oxide Semiconductor) o MOSFET, sono dei componenti elettronici unipolari di grande importanza che hanno permesso lo sviluppo di molti circuiti integrati, sia analogici che logici.

I MOS sono una variante fisica del JFET e sono riconoscibili in due tipi:

MOSFET Enhanncement o ad arricchimento.

MOSFET Depletion o a svuotamento.

per entrambi il canale può essere di tipo p o di tipo n.

MOS ad arricchimento (enhanncement MOS)

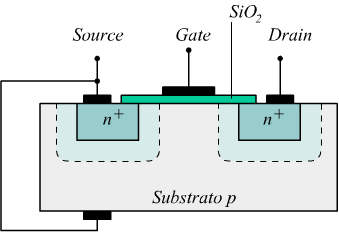

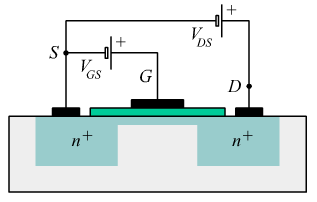

Per fabbricare un MOSFET ad arrichimento, si prende una sbarretta di semiconduttore debolmente drogato di tipo p (substrato). Si ricavano,poi, lateralmente, due zone fortemente drogate di tipo n: il drain ed il source.

Si collega, esternamente, il substrato al terminale di source per evitare che si formi un diodo pn fra source e substrato .

Poi, bisogna inserire sopra il substrato p e tra le due zone uno strato isolante di biossido di silicio SiO2 ponendo su di esso un terzo terminale che sarà il gate.

A questo punto si osserverebbe una zona di svuotamento che penetra maggiormente nella zona p, poco drogata,che non nelle due zone n molto drogate.

Lasciando il terminale di gate flottante, anche se colleghiamo una batteria VDD fra drain e source non si

stabilisce alcun passaggio di cariche elettriche perchè le due zone n+ risultano comunque separate presentando una altissima resistenza.

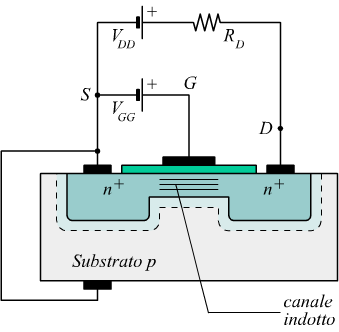

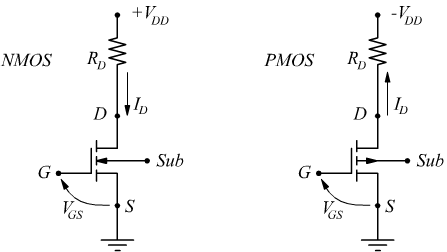

Polarizzando l’NMOS come indicato in figura qui a fianco

si avrebbe VGS>0 e VDS>0 : si produce un campo elettrico che si distribuisce uniformemente sotto l’elettrodo di gate e che penetra nella zona p sottostante; in questa zona si vengono ad accumulare elettroni, che sono i portatori di maggioranza, ne consegue che fra il drain ed il source viene a crearsi un percorso conduttivo: un canale.

Applicando ora, una tensione positiva VDS<VGS si può ottenere un passaggio di una corrente di drain ID fra drain e source.

Perchè si produca questo fenomeno, bisogna che:

1) VGS>VT con VT=tensione di soglia (1÷6 V).

2) VDS<VGS per non alterare l’uniformità del canale.

Siamo in presenza di un dispositivo comandato in tensione in cui, a differenza di un JFET, il canale non è preformato in fase di fabbricazione ma viene prodotto dalla polarizzazione.

Bisogna specificare che il collegamento esterno fra source e substrato realizzabile da un operatore, può essere previsto e realizzato internamente al dispositivo dal costruttore.

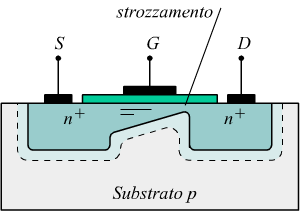

Aumentando il valore di VDS con VGS>VT si osserva un fenomeno analogo a quello visto nel JFET: i due campi elettrici in prossimità delle zone n+ si sommano, dando luogo ad una distribuzione di potenziale, non più uniforme bensì a forma di cuneo; con addensamento di cariche vicino al source e rarefazione verso il drain.

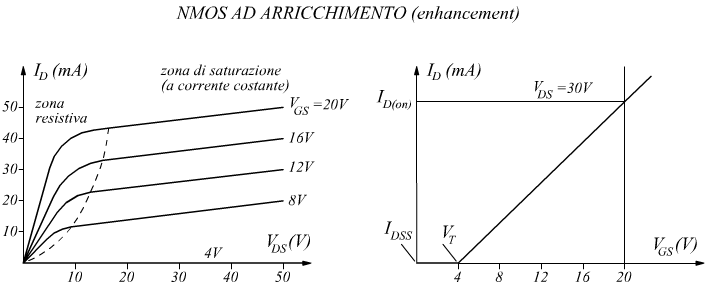

Per valori bassi di VDS il canale si comporta in modo resistivo (zona resistiva).

Quando VDS supera qualche volt, si manifesta ( come nel caso del JFET ) il fenomeno dello ‘strozzamento’ del canale (pinch-off).

La corrente ID a questo punto, aumenta ancora, ma in modo meno sensibile rispetto la zona resistiva: siamo entrati nella zona di saturazione ( a corrente costante) .

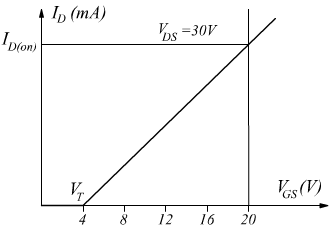

Sulle caratteristiche di ingresso si nota come incrementando la VGS aumenta, in modo lineare, l’effetto indotto sugli elettroni che costituiscono il canale che si allarga, aumentando la corrente ID a parità di VDS.

Dalle caratteristiche di ingresso si vede come per mandare in conduzione il transistor sia necessaria la condizione:

VGS>VT

Sulle caratteristiche di uscita si nota la linea tratteggiata che delimita la zona resistiva dalla zona di saturazione; su questa curva viene raggiunta la condizione di pinch-off per la quale vale la relazione

VDS = VGS – VT

VGS=9 V

VDS=6 V

VT=3 V

VDS<VGS-VT

Un tentativo (approssimativo) di descrivere gli effetti della polarizzazione del transistor sulla geometria del canale è rappresentato qui a sopra.

Si riconosce l’ingresso in zona di saturazione dato dalla condizione:

VDS > VGS – VT

che caratterizza il fenomeno dello ‘strozzamento’ del canale sul lato del drain. Il valore della corrente transitante è proporzionale alla sezione minore del canale.

In definitiva, per ogni caratteristica crescente all’aumentare di VGS il MOS si comporta

• alla sinistra del pinch-off come un dispositivo a resistenza costante

• alla destra del pinch-off come un dispositivo a corrente costante.

Si può dire che il comportamento del MOS è analogo a quello del JFET.

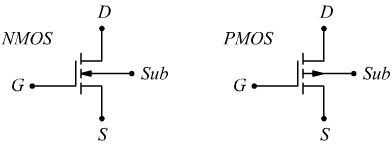

qui a fianco i simboli elettrici di un NMOS

e di un PMOS ad arricchimento.

I parametri statici più importanti del MOS ad arricchimento sono:

• Tensione di soglia VT : il valore dell VGS al di sotto del quale la corrente ID è trascurabile.

• IDS(on): il valore della ID in zona di saturazione in corrispondenza di un determinato valore, piuttosto elevato di VGS (ad es. VGS=25V).

• IDSS e ID(off):indicano la corrente di drain per VGS=0; il suo valore è ovviamente molto basso perché per questa tensione di gate il canale non è ancora formato.

• rDS(on): la resistenza tra drain e source nella regione di funzionamento resistiva.

MOS a svuotamento (depletion MOS)

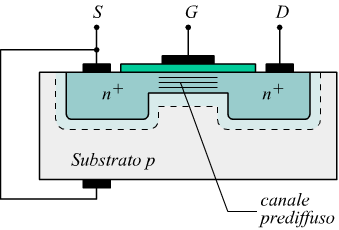

Il MOSFET a svuotamento è una variante fisica e circuitale del MOS ad arricchimento visto prima: si tratta sempre di un dispositivo unipolare disponibile sia di tipo p che di tipo n, in cui però il canale è preformato (come nel JFET).

Con questa struttura, essendo il drain ed il source già in collegamento, è possibile ottenere a secondo della polarità della VGS sia un restringimento che un allargamento del canale.

Per VGS=0 la corrente ID può scorrere dal drain al source spontaneamente, in presenza di una VDS positiva.

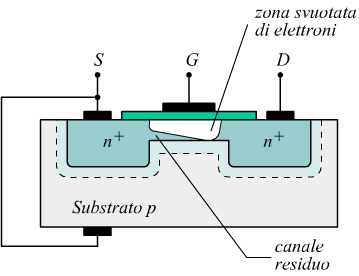

In queste condizioni, il canale è sede di una distribuzione di potenziale crescente verso il drain, quindi, il campo elettrico fra gate e canale tende a rinforzarsi dalla parte del drain. Dato che il gate è ad una tensione inferiore a quella del canale, il campo vi induce cariche positive che sono più numerose dalla parte del drain. Queste cariche positive neutralizzano i portatori positivi e quindi svuotano il canale di portatori liberi restringendolo dalla parte del drain, come si vede nel disegno.

Aumentando VDS si raggiunge lo strozzamento e la corrente entra nella sua zona di saturazione.

Rendendo VGS negativa, lo strozzamento viene raggiunto per valori minori di VDS.

Il funzionamento è identico a quello del JFET.

La struttura del MOS a svuotamento a canale p è analoga; il substrato è però dogato di tipo n e le diffusioni fra source e drain sono di tipo p.

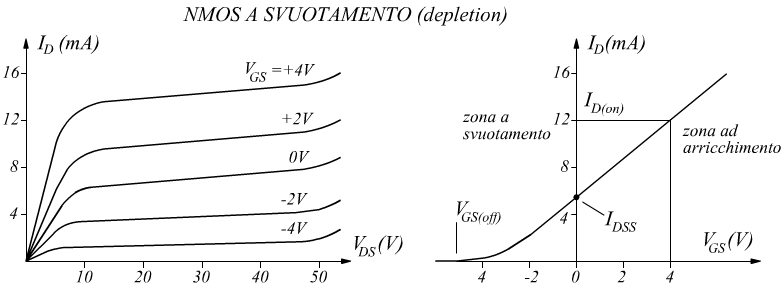

Nella seguente figura sono illustrate le caratteristiche di uscita e di trasferimento (transcaratteristica) di un NMOS a svuotamento

Dalle caratteristiche di ingresso si vede che il MOS a svuotamento può anche funzionare come MOS ad arricchimento; basta applicare al gate una tensione VGS>0.

In questo caso il canale si allarga per le cariche negative indotte dal campo elettrico, permettendo un aumento della corrente di drain.

Queste considerazioni relative all’NMOS sono valide anche per il PMOS; bisogna però ricordarsi che le correnti presentano verso opposto e le tensioni ( anche quelle di alimentazione) sono negative.

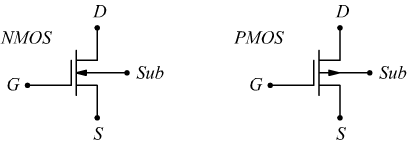

qui a fianco i simboli elettrici di un NMOS

e di un PMOS a svuotamento.

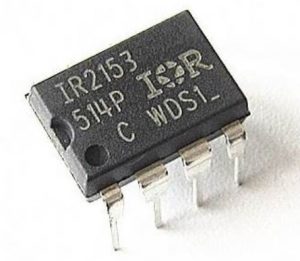

MOSFET come interruttore

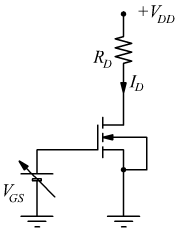

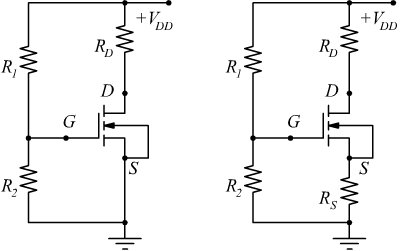

Come detto, il MOS è un dispositivo sia analogico che digitale, quindi può essere usato come interruttore elettronico, in commutazione,oppure come amplificatore,nella zona di saturazione. Nei circuiti integrati digitali viene impiegato in commutazione mentre come componente discreto trova impiego in entrambi i modi. La configurazione base del MOS operante come interruttore è disegnata qui:

nonostante sia rappresentato solo il modello ad arricchimento le valutazioni che seguono sono valide anche per il modello a svuotamento.

| Stato OFF: per portare in interdizione un NMOS | |

| VGS < VT | ad arricchimento |

| VGS < VGS(off) | a svuotamento |

| Stato OFF: per portare in interdizione un PMOS | |

| VGS > VT | ad arricchimento |

| VGS > VGS(off) | a svuotamento |

Stato ON: Per portare in piena conduzione un NMOS occorre fornire una VGS sufficientemente alta, in modo da portare il dispositivo in zona resistiva. Lo stesso vale per un PMOS, solo che in questo caso la VGS sarà negativa.

Esempio:

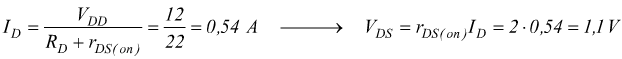

Nel circuito dell’NMOS qui indicato si ha VT=3 V rDS(on)=2Ω ID(on)=2 A.

Sapendo che la tensione di alimentazione VDD=12 V ed RD=20Ω calcola i valori delle tensioni e delle correnti negli stati ON e OFF del transistor.

Soluzione:

Per avere l’interdizione basta che sia VGS<VT=3 V

Per semplicità si pone VGS=0 V e si ha ID=0 con VDS=VDD=12 V

Se proviamo a mettere VGS=10V

Il transistor è in conduzione in zona resistiva anche perchè ID<ID(on) che sarebbe la corrente che interesserebbe il MOS se questo fosse in zona di saturazione.

Il MOS non è ancora in zona di saturazione anche perchè la condizione

VDS > VGS – VT non è soddisfatta.

Polarizzazione di un MOSFET

Se consideriamo un MOS ad arricchimento ( ma le stesse considerazioni valgono per un NMOS a svuotamento ) la polarizzazione può essere costituita dalla classica rete di autopolarizzazione con partitore sul gate.

La rete può eventualmente essere dotata della resistenza di stabilizzazione rispetto alla deriva termica RS.

Si è visto sopra, come il legame fra ID e VGS nella regione di saturazione, rappresentato graficamente dalla caratteristica di ingresso. Si tratta di una linea retta che può essere espressa con buona approssimazione dalla

![]()

Normalmente la K non è dichiarata nei datasheets ma può essere facilmente ricavata ponendo nell’ equazione i valori ID e di VGS relativi a un punto noto della curva, per esempio ID(on) e la VGS corrispondente.

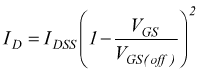

Nel caso di un MOS a svuotamento, la transcaratteristica già vista può essere rappresentata analiticamente dalla stessa relazione per i JFET.

Nei MOS a svuotamento il gate deve essere polarizzato negativamente rispetto al source, così come nei JFET. I circuiti di polarizzazione sono gli stessi usati per i JFET.

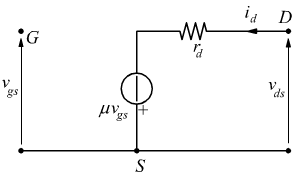

Modello del MOS per piccoli segnali

Il modello valido per il JFET è valido anche per il MOS sia ad arricchimento che a svuotamento.

La transconduttanza gm dei MOS , pur essendo dello stesso ordine di grandezza ma può raggiungere valori anche maggiori

(da 0,2÷20 mA/V).

Al contrario la resistenza di drain rd è decisamente inferiore a quella del JFET, anche se non sempre è possibile trascurarla.

Anche per i MOS, i datasheets forniscono la transconduttanza per un determinato punto della caratteristica mutua. Per il MOS a svuotamento viene ancora fornito il valore di gm ed di gmo per VGS=0.

Si può ottenere il valore di gm in un punto di funzionamento diverso utilizzando le stesse formule viste per il JFET.

Per i MOS ad arricchimento, chiamando con V’GS e con I’D i valori in corrispondenza dei quali è fornita la transconduttanza che viene indicata g’m , si hanno le seguenti relazioni:

Dove gm VGS e ID sono i valori relativi a un punto di funzionamento qualsiasi.

Nel caso in cui non venga fornito g’m è possibile ricavare gm mediante la formula

![]()

Grazie.